当前,人工智能正以前所未有的深度重塑半导体产业链的核心环节,而作为芯片设计的 “引擎”,EDA(电子设计自动化)领域正经历着从传统规则驱动向数据智能驱动的范式迁移。主流EDA厂商纷纷加大AI工具研发的投入,通过引入AI技术赋能EDA工具,助力芯片设计,这场由AI引发的技术变革,不仅在重构芯片设计的效率边界,更在重新定义 EDA 工具的核心竞争力。

在日前举行的CadenceLIVE中国用户大会上,Cadence全球研发副总裁兼三维集成电路设计分析事业部总经理Ben Gu(顾鑫),围绕AI时代算力需求催生EDA领域的变革,分享了Cadence在3D-IC以及AI领域的创新实践。

AI推动EDA工具进化

近年来,AI引发的算力革命,在对人们的工作和生活产生影响的同时,也为半导体行业带来机遇和挑战。IDC的研究数据显示,由于AI的驱动,2030年半导体市场规模将突破1万亿美元。

AI不仅驱动了芯片设计的进步,在算力需求下,也让芯片设计变得更加复杂。更多的晶体管堆叠,更复杂的3D集成电路系统,以及领先的晶圆代工厂推动更先进的工艺节点和制造方案等,都对芯片设计系统带来巨大的挑战。

在Ben看来,过去二三十年EDA行业发展迅速的重要的原因之一在于受到摩尔定律驱动,而AI对于推动芯片设计流程的重塑将具有同样的效能。新的EDA工具用来发展新一代的AI芯片,提升新一代的AI性能。同样,新的AI技术也会被用于发展下一代的EDA技术提升EDA的性能。如此往复,推动整个行业健康加速向前发展。

“据我们统计,2025年,已经有超过一半的客户在使用Cadence提供的不同形式的AI工具来进行芯片设计。预计到2030年,AI在芯片设计流程中的占比将超过80%,从而使整个设计流程大幅自动化。其中,AI智能体将发挥重要作用。未来两三年,除了为客户提供EDA工具,我们更希望能够提供EDA的AI智能体。”Ben表示。

应对算力挑战的3D-IC

人工智能的发展,特别大型神经网络模型的训练和推理,对算力提出极高要求。传统的二维集成电路(2DIC),逐渐显现出局限性,面临 “内存墙”“互连瓶颈” 和 “散热极限” 等多重阻力,无法满足人工智能对高密度计算与高带宽内存的紧耦合要求。

因此,3D-IC成为行业在应对AI时代算力挑战时的突破方向,通过2.5D、3D或3.5D的堆叠来进一步提高芯片算力和芯片之间的带宽。比如,台积电一直在积极推进CoWoS等堆叠技术的创新演进。而其下一代系统级芯片封装技术 SoW-X(System-On-Wafer),通过在Wafer上集成数十个芯片,实现RDL互联,将能够非常显著地提升整体芯片算力。

在Ben看来,3D-IC将成为未来五到十年非常热门的话题并带来革命性的创新。同时,由于系统的复杂性,比如多个芯片堆叠在极小的芯片上将产生巨大功耗等,也为3D-IC设计带来更多挑战。为了让3D-IC的设计符合需求,需要解决包括散热、时序(Timing)、压降分析(IR drop)等一系列问题。

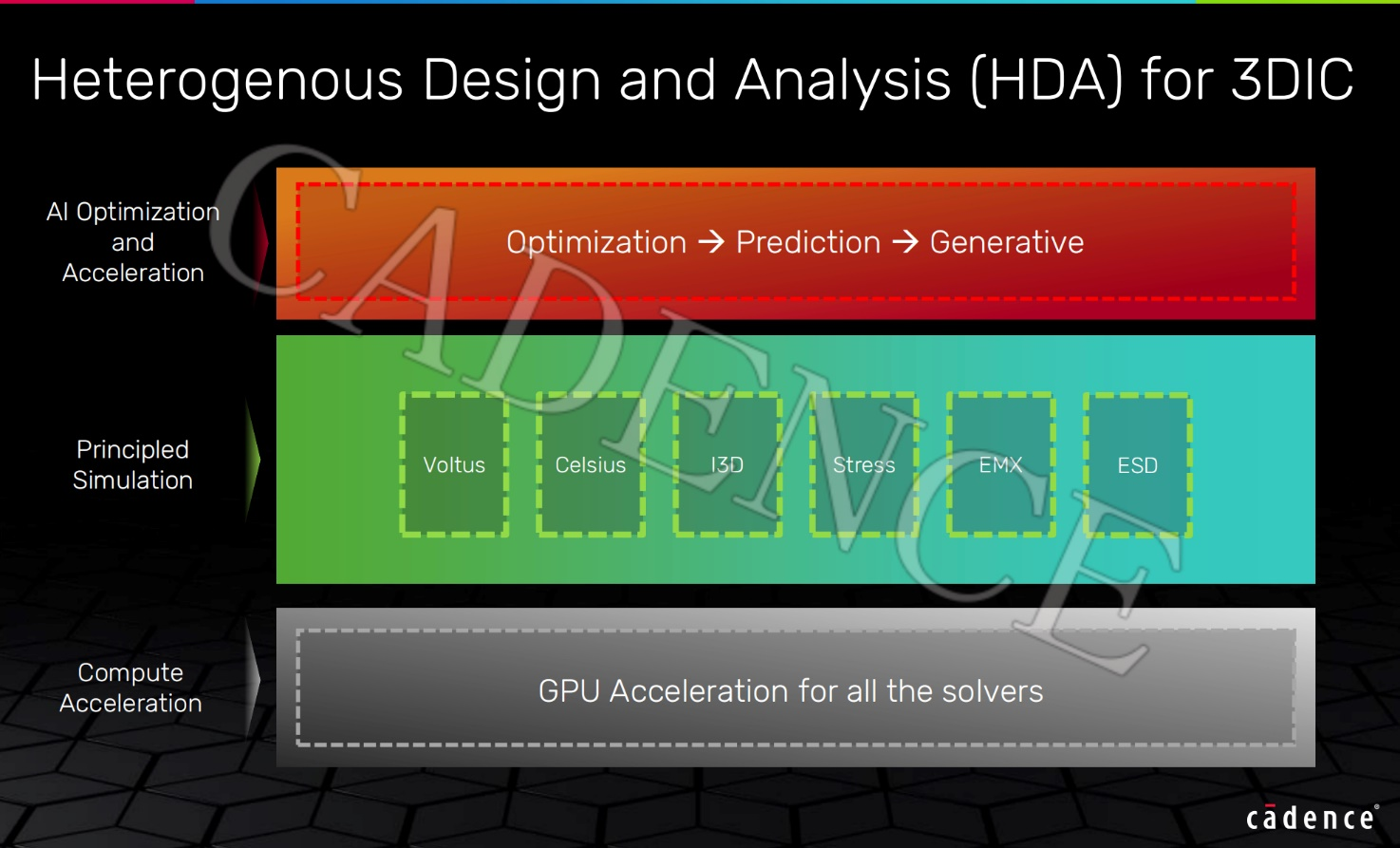

据Ben介绍,今年3月,Cadence将与3D-IC相关的设计分析产品重新组合在一起,成立了全新的事业部HDA(Heterogeneous Design Analysis),通过三个层面的创新工作,应对3D-IC所带来的高速发展机遇和挑战。

HDA通过集成各种3D-IC需要的分析工具(电、磁、热、力等),并与Cadence的设计平台整合在一起。此外,我们还计划将所有分析产品都移植到GPU上,实现大规模的性能加速,进而训练AI模型实现进一步加速,帮助设计工程师可以用AI模型来探索设计空间并得到最优化的设计结果。

Integrity™:助力3D-IC设计

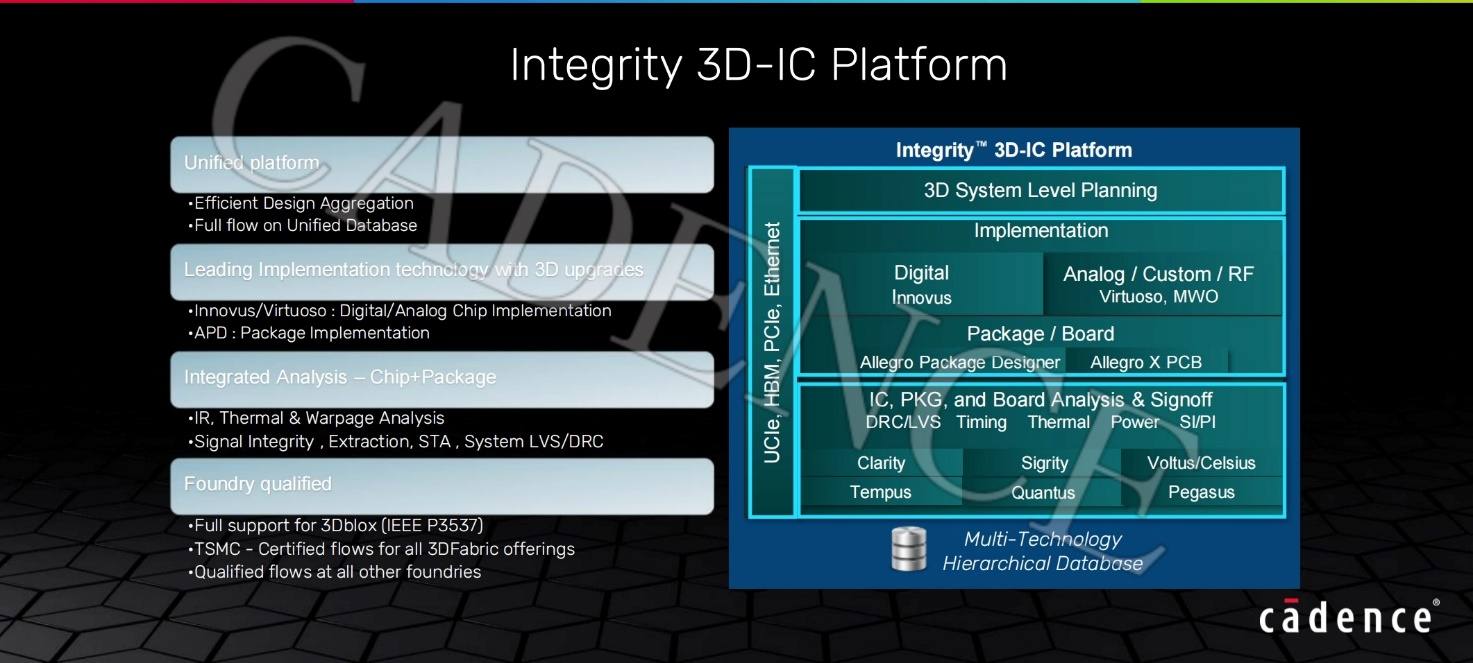

在产品侧,为应对3D-IC设计所带来的挑战,2021年,Cadence推出Integrity™ 3D-IC设计平台,通过集成统一的操作界面和数据库,将所有与3D-IC相关的设计数据(包括routing、placement等)融合在一起,为客户提供一站式EDA工具服务。

Integrity™不仅同Cadence领先的数字和模拟领域的工具Innovus和Virtuoso紧密结合,还能与Cadence的各种分析工具,尤其是多物理场仿真分析工具结合进行系统分析,从而优化设计。

据Ben介绍,过去几年,Cadence持续投入提升Integrity™的性能和兼容能力,目前已实现和主要的晶圆厂伙伴及封测厂商的紧密合作,且已被所有的行业头部客户采用,包括领先的AI厂商和服务器厂商。

3D-IC 通过堆叠多层芯片实现高密度集成,但不同芯片因功能、工艺、尺寸差异大,且堆叠方式(如 TSV 位置、RDL 布线、散热路径等)会直接影响整体性能。因此,Integrity™ 3D-IC中的System Planner(系统规划器)便十分重要,能够在芯片设计初始阶段提供对整个系统的全局规划,从而得到最佳的系统表现。同时,Integrity™ 3D-IC平台支持Cadence自研布线技术,能够实现芯片间复杂线路的连接,考虑到先进封装存在各种复杂布线需求,Integrity™ 3D-IC还支持自动布线和自动分组。

此外,针对Cadence的多物理场仿真解决方案,Integrity™ 3D-IC能够实现这些工具在芯片中的内置和深度联动,帮助客户验证结果并优化设计。

Voltus:全新升级

Voltus是Cadence推出的一款电源完整性分析工具,已有11年历史。据Ben介绍,今年Cadence计划推出新一代Voltus产品——Voltus Infinity,大幅提升Voltus内部算法,包括针对GPU加速的XD(neXt generation Dynamic)、针对广泛仿真分析覆盖度的算法XC (eXtreme Coverage),以及针对可用性分析和调试的XU (neXt generation User interface)等三项关键技术。

据了解,Voltus-XD将Wafer中所有的IR drop(压降分析)仿真引擎从CPU迁移到GPU,通过采用Voltus的GPU分析引擎实现加速,从而大幅缩短模拟时间。

今年5月,Cadence推出了超级计算机——Millennium M2000,将 NVIDIA GPU 技术与 Cadence 的全套计算软件及 AI 功能相结合(包括XD技术),与传统CPU集群需要两周的时间相比,工程师现可在一天内完成芯片级电源完整性模拟。

在提升仿真分析覆盖度方面,过去因为仿真性能受限等原因,通常芯片设计在进行Voltus和IR drop仿真时,只能覆盖20个或100个时钟周期(Cycle)以及芯片的少部分应用。而升级后的仿真引擎Voltus-XC,可以将时钟周期提升至百万级别,使得芯片设计厂商能够进行更充分的验证,从而降低芯片设计风险,让签核(Sign Off)环节更加有保证。

在可用性以及可调试性方面,Voltus -XU采用了新一代的用户界面,同时引入了AI助手(集成Cadence大语言模型和JedAI),便于用自然语言同EDA图形界面互动,debug、查询设计结果。

AI赋能多物理场仿真

相比传统 2D 芯片,3D-IC的优势是 “缩小面积、提升性能、降低功耗”,但堆叠结构也直接带来了大规模互联产生的散热和“机械失效”(Mechanical Failure)等方面的新问题。

在Cadence 的 EDA 工具生态中,Thermal/Mechanical(热学 / 机械应力分析工具) 是其 “多物理场解决方案(Multiphysics Solution)” 的重要组成部分。

Ben Gu表示,准确的Thermal仿真对3D-IC设计至关重要,Cadence的Celsius Thermal Solver自2019年面世以来,经过多年打磨已完全能够应对3D-IC的设计挑战。Celsius能够同Innovus、Voltus有非常紧密地结合,从Voltus取得Power的数据后进行仿真分析,再将结果反馈给Voltus得到更准确的IR drop结果。目前,Celsius 3D-IC方案已经被多家头部客户采用。

而为应对机械失效等方面的挑战,据Ben介绍,Cadence即将推出Tenacity Stress Solver。为应对3D-IC多达数百万个凸块(bump)所带来的复杂应力(stress) 分析问题,Tenacity 能够提供层级化的解决方案(Hierarchical solution),借助于AI和GPU的技术加速,在不牺牲精度的情况下,提供快速的仿真解决方案。

此外,针对常规3D-IC仿真较为耗时等问题,Cadence还即将推出Celerity AI 加速解决方案,加快设计流程提升设计表现。Celerity可以通过Cadence内部生成的大量设计数据训练仿真大模型,再交由客户微调优化,最终用神经网络替代传统仿真流程,提升芯片设计效率。

结语

从 Cadence 在 AI 时代的 EDA 创新实践中,能够清晰地看到 AI 正从 “辅助工具” 升级为驱动 EDA 工具研发与芯片设计变革的 “核心引擎”。

在领先的EDA厂商积极创新探索下,由AI 赋能的 EDA 工具正助力芯片设计实现“降维破局”。未来,随着 EDA AI 智能体的进一步落地、多物理场仿真与 AI 的进一步融合,EDA 工具将从 “自动化” 迈向 “自主化”,不仅能帮助芯片设计团队更高效地突破先进工艺与复杂集成的技术壁垒,更将持续夯实 AI 芯片创新的底层根基,最终推动半导体行业在算力革命中实现更具想象力的突破。