1.中国科学院研发出超采样成像技术 实现像素“分割”成像;

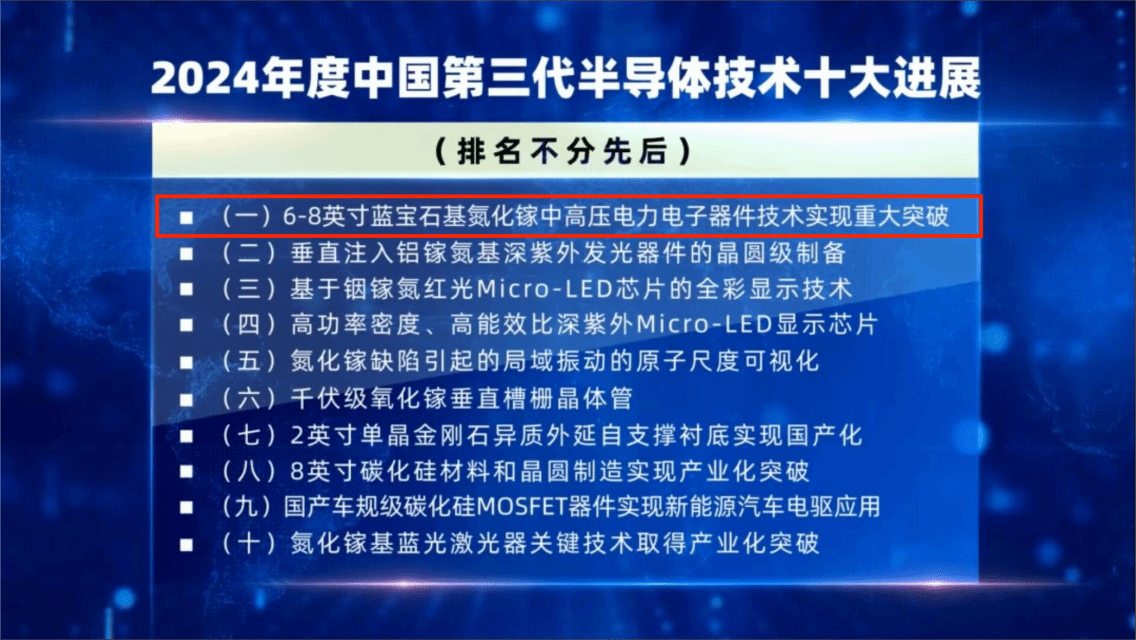

2.西安电子科技大学第三代半导体创新中心成果入选IFWS 2024中国第三代半导体技术十大进展;

3.从平面晶体管到FinFET的演变;

1.中国科学院研发出超采样成像技术 实现像素“分割”成像;

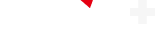

数字图像传感器的像素规模与性能是影响天文、遥感等领域成像质量的核心。当前,图像传感器芯片制造已趋近技术极限。中国科学院空天信息创新研究院张泽研究团队首次提出超采样成像概念。近日,相关研究成果发表在《激光与光子学评论》(Laser & Photonics Reviews)上。

数字图像传感器的工作原理本质上是对光场进行采样显像的过程,类似于传统的胶卷。根据奈奎斯特采样定律,一个信息光场周期至少需要两个像素采样才会不丢失信息。因此,图像传感器的像素分辨率是图像显示的细节极限。超采样成像是突破像素分辨率极限,利用少数像素传感器实现大规模像素显像能力的技术。

自数字图像传感器取代胶卷以来,成像技术一直受到传感器采样极限的困扰。人类制造的数字图像传感器在像素尺寸、数量规模和响应均匀性上不及胶卷。依据目前的制造水平,数字图像传感器的像素分辨率和成像质量难以大幅提升。超采样成像技术规避了芯片制造水平的限制,为突破像素分辨率成像提供了一条鲁棒性很强的技术途径。

在实现原理上,该团队采用稳态激光技术扫描数字图像传感器,通过稳态光场表达式和输出图像矩阵的关联关系,精确求解出图像传感器像素内量子效率分布。当使用相机拍摄动态目标或者移动相机拍摄静态场景时,通过获取的像素内量子效率和像素细分算法,可以突破原始像素分辨率,实现超采样成像。稳态激光技术是由该团队首创的锋芒稳态激光技术演化而来,在原理上具有极稳定的光场形式。

超采样成像技术目前可以将像素规模提高5×5倍,即利用1k×1k的芯片可以实现5k×5k像素分辨率的成像。随着标校精度提高,像素分辨率具有提升空间。打个比方,原有像素是一个方块,通过这一技术可以将像素分割,等效变成25个像素(方块),对应着像素规模提升了25倍。

该技术具有广阔应用发展潜力。以红外图像传感器为例,市场化的成像芯片分辨率一般在2k×2k以下,3k×3k、4k×4k的成像芯片尚未有成熟的商用产品,而采用超采样成像技术则可以利用2k×2k芯片实现8k×8k以上的像素分辨率,在光学遥感、安防等成像领域具有应用前景。

目前,这一技术在室内、室外对无人机、建筑、高铁、月亮等目标进行了成像试验,展现出良好的技术鲁棒性。

超采样成像技术流程示意图

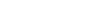

2.西安电子科技大学第三代半导体创新中心成果入选IFWS 2024中国第三代半导体技术十大进展;

11月18-21日,第十届国际第三代半导体论坛&第二十一届中国国际半导体照明论坛(IFWS&SSLCHINA2024)在苏州召开。此次论坛汇聚了众多院士及产业链各环节的逾千名代表,共同探讨第三代半导体技术的最新发展与未来趋势。在11月19日开幕式上,2024年度中国第三代半导体技术十大进展重磅揭晓,这些进展不仅代表了行业的技术前沿,也预示着产业发展的新方向,受到了与会代表的广泛关注和热烈讨论,其中广州第三代半导体创新中心“6-8英寸蓝宝石基氮化镓中高压电力电子器件技术实现重大突破”入选2024年度中国第三代半导体技术十大进展。

西安电子科技大学广州第三代半导体创新中心郝跃院士课题组张进成教授、李祥东教授团队成功攻克了6-8英寸蓝宝石基GaN电力电子器件的外延、设计、制造和可靠性等系列难题,基于低翘曲超薄外延、高质量双层钝化等创新方法,实现1200V和1700 V高性能 GaN HEMT中试产品开发,通过HTRB、HTGB等可靠性评价,成果应用于致能科技等公司系列产品中,显著推动蓝宝石基GaN成为中高压电力电子器件方案的有利竞争者。

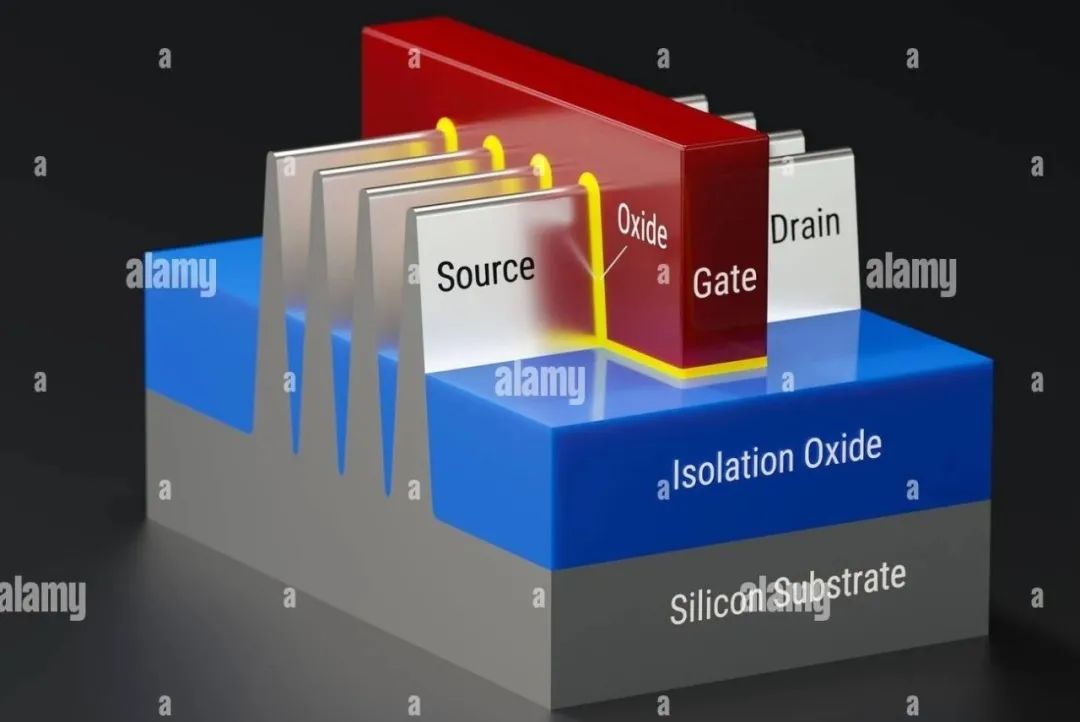

3.从平面晶体管到FinFET的演变;

在90纳米制程之前,每一代集成电路技术节点的缩放不仅带来了更高的器件密度,还提升了器件性能。然而,当CMOS IC从90纳米发展到65纳米节点时,缩放并未改善器件性能:它只增加了器件密度。这一变化的主要原因是栅氧化层的厚度无法再继续减薄,因为隧道效应引起的泄漏电流成为了一个不可忽视的问题。

平面晶体管的局限性

MOSFET(金属氧化物场效应晶体管)的一个重要性能参数是驱动电流 Id,其与公式 Id∝μ(K/Tox)(W/L) 成正比。其中:μ 是沟道材料的载流子迁移率(对于NMOS为电子迁移率,对于PMOS为孔穴迁移率)。K 是栅极介质的介电常数。Tox 是栅氧化层的厚度。W 是沟道宽度。L 是沟道长度。

如果仅缩小平面MOSFET的特征尺寸,则 W 和 L 会以相同的比例减小,除非 Tox 同样减小,否则驱动电流不会得到改善。为了降低漏电和功耗,供电电压和阈值电压也会偶尔随栅氧化层厚度一起减小。当 Tox 变得非常薄并接近泄漏和击穿极限时,人们不得不寻找其他方法来提高 Id。

高k/金属栅极(HKMG)技术

为了解决栅氧化层厚度限制的问题,人们引入了高介电常数栅介质和金属栅技术(HKMG)。使用高k材料(如HfSiOxNy)替代传统的SiO2栅介质,可以显著增加栅介质的介电常数K,从而形成更薄的有效氧化物厚度(EOT),进一步提高驱动电流。例如,HfSiOxNy的介电常数 K 可以达到20左右,远高于SiO2的3.9。

在45纳米以下技术中引入了HKMG,这有助于减少EOT并进一步提升器件性能。尽管HKMG技术在一定程度上解决了栅氧化层厚度的问题,但随着技术节点的进一步缩小,平面MOSFET的性能提升遇到了瓶颈。因此,业界开始探索新的晶体管结构,FinFET应运而生。

FinFET的结构

平面MOSFET:平面MOSFET的沟道位于一个平面上。

FinFET:FinFET的沟道呈鳍状,沟道被栅极从三个方向包围。

FinFET的优势

增加沟道宽度:FinFET可以在较小的硅表面面积上实现相同的沟道宽度。通过增加鳍的高度,沟道宽度可以进一步增加,因此可以在不缩小器件特征尺寸的情况下进一步提升器件性能。

减少短沟道效应:FinFET的三维结构有助于更好地控制沟道区,减少短沟道效应,提高晶体管的可靠性和性能。

提高驱动电流:FinFET的三面栅结构可以更有效地控制沟道区,减少漏电,提高驱动电流 Id。

FinFET的制造挑战

蚀刻和清洗:如果鳍太高且纵横比过高,蚀刻和清洗鳍而不引起其坍塌将变得非常困难。

STI填充:填充鳍之间的STI(浅沟槽隔离)的无空洞介电薄膜也将变得非常困难。