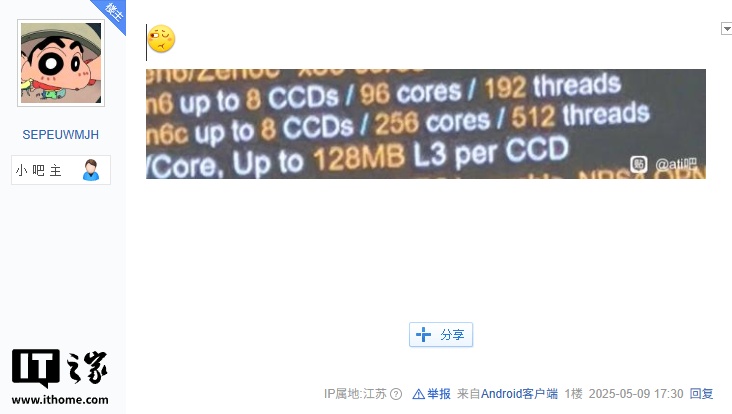

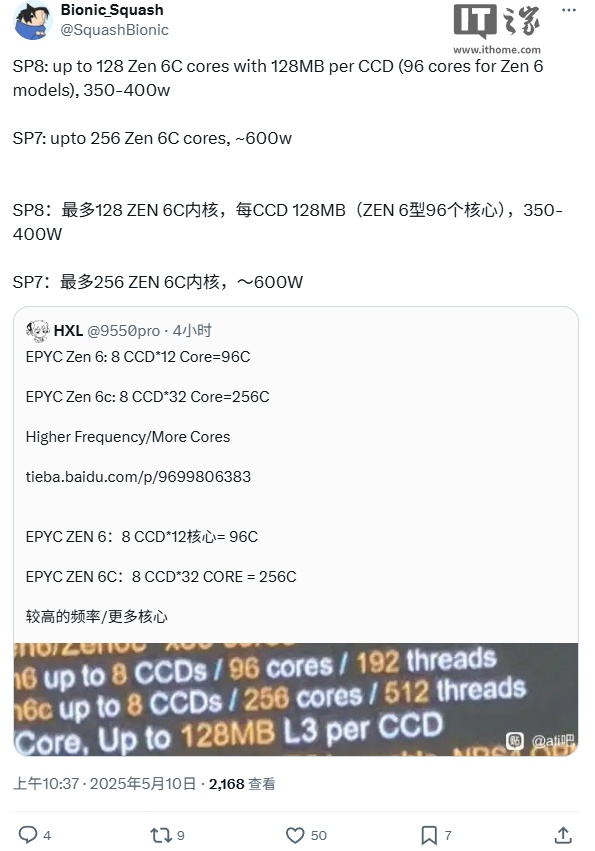

IT之家 5 月 10 日消息,贴吧用户 @SEPEUWMJH 昨日曝光了 AMD 第六代霄龙(EPYC)Venice 处理器的部分信息,@SquashBionic 今日又补充了更多细节。

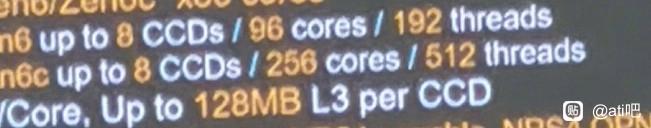

AMD 下一代 EPYC Venice 处理器依然会分为 Zen 6 和 Zen 6C 两种版本,分别注重频率和核心数量,采用 SP7 和 SP8 平台,前者定位高端解决方案,后者则定位入门级服务器解决方案。

该芯片两侧各采用四个 CCD,总共有 8 个 CCD。每个 CCD 包含 12 个 Zen 6 核心或 32 个 Zen 6C 核心,中间有多个 IOD,将进一步扩展服务器平台的 I/O 能力。

@SEPEUWMJH 表示,普通的 Zen 6 版本最多具备 96 核心 192 线程,每个 CCD 配备 48MB L3 缓存,总计 384MB(单核 4MB);而 Zen 6C 版本最高 256 核 512 线程,每个 CCD 配备 128MB L3 缓存,总计 1024MB(单核 4MB),相比 Turin 实现翻倍。

Bionic_Squash 表示,SP7 版本(Zen 6)的 TDP 约为 600W,高于 Zen 5 的 400W;而 SP8 版本(Zen 6C)的 TDP 约在 350-400W 之间。IT之家附对比如下:

EPYC 9006“Venice”搭载 Zen 6C 核心: 256 核 512 线程 / 最多 8 个 CCD

EPYC 9005“Turin”搭载 Zen 5C 核心: 192 核 384 线程 / 最多 12 个 CCD

EPYC 9006“Venice”搭载 Zen 5 核心:96 核 192 线程 / 最多 8 个 CCD

EPYC 9005“Turin”搭载 Zen 5 核心:96 核 192 线程 / 最多 16 个 CCD

| AMD EPYC Venice | AMD EPYC Turin-X | AMD EPYC Turin-Dense | AMD EPYC Turin | AMD EPYC Siena | AMD EPYC Bergamo | AMD EPYC Genoa-X | AMD EPYC Genoa | AMD EPYC Milan-X | AMD EPYC Milan | AMD EPYC Rome | AMD EPYC Naples | |

|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 家族 | EPYC 9006 | EPYC 9005 | EPYC 9005 | EPYC 9005 | EPYC 8004 | EPYC 9004 | EPYC 9004 | EPYC 9004 | EPYC 7004 | EPYC 7003 | EPYC 7002 | EPYC 7001 |

| 发布时间 | 2026? | 2025 | 2025 | 2024 | 2023 | 2023 | 2023 | 2022 | 2022 | 2021 | 2019 | 2017 |

| CPU 架构 | Zen 6 | Zen 5 | Zen 5C | Zen 5 | Zen 4 | Zen 4C | Zen 4 V-Cache | Zen 4 | Zen 3 | Zen 3 | Zen 2 | Zen 1 |

| 制程 | 2nm TSMC | 4nm TSMC | 3nm TSMC | 4nm TSMC | 5nm TSMC | 4nm TSMC | 5nm TSMC | 5nm TSMC | 7nm TSMC | 7nm TSMC | 7nm TSMC | 14nm GloFo |

| 平台 | SP7 | SP5 | SP5 | SP5 | SP6 | SP5 | SP5 | SP5 | SP3 | SP3 | SP3 | SP3 |

| 插槽 | TBD | LGA 6096 (SP5) | LGA 6096 (SP5) | LGA 6096 | LGA 4844 | LGA 6096 | LGA 6096 | LGA 6096 | LGA 4094 | LGA 4094 | LGA 4094 | LGA 4094 |

| 最大核心数 | 96 | 128 | 192 | 128 | 64 | 128 | 96 | 96 | 64 | 64 | 64 | 32 |

| 最大线程数 | 192 | 256 | 384 | 256 | 128 | 256 | 192 | 192 | 128 | 128 | 128 | 64 |

| 最大 L3 缓存 | TBD | 1536 MB | 384 MB | 384 MB | 256 MB | 256 MB | 1152 MB | 384 MB | 768 MB | 256 MB | 256 MB | 64 MB |

| 芯片设计 | 8 CCD's (1 CCX per CCD) + 2 IOD? | 16 CCD's (1CCX per CCD) + 1 IOD | 12 CCD's (1CCX per CCD) + 1 IOD | 16 CCD's (1CCX per CCD) + 1 IOD | 8 CCD's (1CCX per CCD) + 1 IOD | 12 CCD's (1 CCX per CCD) + 1 IOD | 12 CCD's (1 CCX per CCD) + 1 IOD | 12 CCD's (1 CCX per CCD) + 1 IOD | 8 CCD's (1 CCX per CCD) + 1 IOD | 8 CCD's (1 CCX per CCD) + 1 IOD | 8 CCD's (2 CCX's per CCD) + 1 IOD | 4 CCD's (2 CCX's per CCD) |

| 内存支持 | DDR5 | DDR5-6000? | DDR5-6400 | DDR5-6400 | DDR5-5200 | DDR5-5600 | DDR5-4800 | DDR5-4800 | DDR4-3200 | DDR4-3200 | DDR4-3200 | DDR4-2666 |

| 内存通道 | 16-通道 | 12 通道 | 12 通道 | 12 通道 | 6 通道 | 12 通道 | 12 通道 | 12 通道 | 8 通道 | 8 通道 | 8 通道 | 8 通道 |

| PCIe | TBD | TBD | 128 PCIe Gen 5 | 128 PCIe Gen 5 | 96 Gen 5 | 128 Gen 5 | 128 Gen 5 | 128 Gen 5 | 128 Gen 4 | 128 Gen 4 | 128 Gen 4 | 64 Gen 3 |

| 最大 TDP | ~600W | 500W (cTDP 600W) | 500W (cTDP 450-500W) | 400W (cDP 320-400W) | 70-225W | 320W (cTDP 400W) | 400W | 400W | 280W | 280W | 280W | 200W |