近日,英伟达与英特尔两大芯片巨头的联姻引爆了市场。

这场旨在融合AI加速计算与x86生态优势的战略联盟,其核心支点直指NVIDIA NVLink技术的架构互联能力——这一曾与PCIe分庭抗礼的高速互连方案,如今借由英特尔的入局获得了前所未有的权重与影响力。

相较于英特尔主导超二十年的PCIe标准,NVLink以数倍的带宽跃升与延迟突破等性能优势,在AI训练、超大规模计算等场景中展现出碾压性竞争力,正让PCIe技术路线面临前所未有的挑战。

更耐人寻味的是,作为PCIe标准的奠基者,英特尔此次选择拥抱NVLink的举动更具象征意义。这种技术路线的“自我革新”,如果真的能按照计划推进,不仅意味着CPU与GPU的互连范式将迎来重构,更可能会对让长期依赖PCIe高速信号补偿需求的Retimer芯片产生影响。(备注:我们所做的假设前提是双方计划真正实施,至于影响幅度大小,我们没有具体分析,但希望能够就技术的变动带来新的观察,仅供参考。)

在这场由NVLink掀起的技术路线重构与替代浪潮中,正应了那句“有人欢喜有人愁”——英伟达借合作打通了AI基础设施的x86生态通路,英特尔则凭定制化产品拓展了在高端计算领域的边界,双方无疑是“欢喜”的阵营;反观曾依托PCIe高速信号补偿需求站稳产业链的PCIe Retimer芯片,却恰恰沦为了“愁”的一方,成为这场产业迭代里最先直面冲击的角色。

PCIe Retimer的“立身之本”

要想了解Retimer芯片,我们需要先了解PCIe总线。

众所周知,总线是为电脑/服务器主板上不同的硬件进行互相数据通信的“道路”,单位时间内数据传输量被称为带宽,即每秒传输的比特数。总线对硬件间数据传输速度起决定性作用,在服务器对计算速度和时延等要求不断提高背景下,计算机总线标准也在不断迭代。

目前最主流的总线为PCIe协议(PCI-Express),由Intel在2001年提出,以替代旧的PCI、PCI-X和AGP等总线标准。PCIe协议近年来发展迅速,传输速率基本上实现了每3-4年翻倍增长,并保持良好的向后兼容特性。

尤其是在人工智能算力需求爆发式增长的今天,数据中心内部的高速数据传输正面临前所未有的压力。这推动了PCIe协议快速发展,从 PCIe 3.0、4.0,一路跃升至5.0、6.0时代,传输速率从 8GT/s、16GT/s 不断翻倍至 32GT/s、64GT/s。

然而,随着通信速率逐代提升,信号衰减问题愈发严重。在PCIe标准迭代中,一方面随着应用不断发展推动着PCIe标准迭代更新,速度不断翻倍;另一方面由于服务器的物理尺寸受限于工业标准并没有很大的变化,导致整个链路的插损从PCIe3.0时代的22dB增加到了PCIe4.0时代的28dB,并进一步增长到了PCIe5.0时代的36dB。如何解决PCIe信号链路的插损问题,提高PCIe信号传输距离是业界面临的重要问题。

Retimer的出现是PCIe发展到一定阶段的必然产物。在PCIe 4.0及更早版本之前,数据传输速率相对较低,对信号完整性的要求不高。但到了PCIe 5.0、PCIe 6.0时代,数据传输速率提高到32GT/s、64GT/s,信号衰减和抖动问题开始愈发突出,插入损耗也随之增加。

PCIe规范有精确的插入损耗预算,例如,PCIe 6.0版本的插入损耗预算为32dB,意思就是在设计时必须确保信号在传输过程中的总损失不超过32dB,以保持信号质量。

对此,PCIe Retimer芯片成为解决信号衰减问题的主流方案。

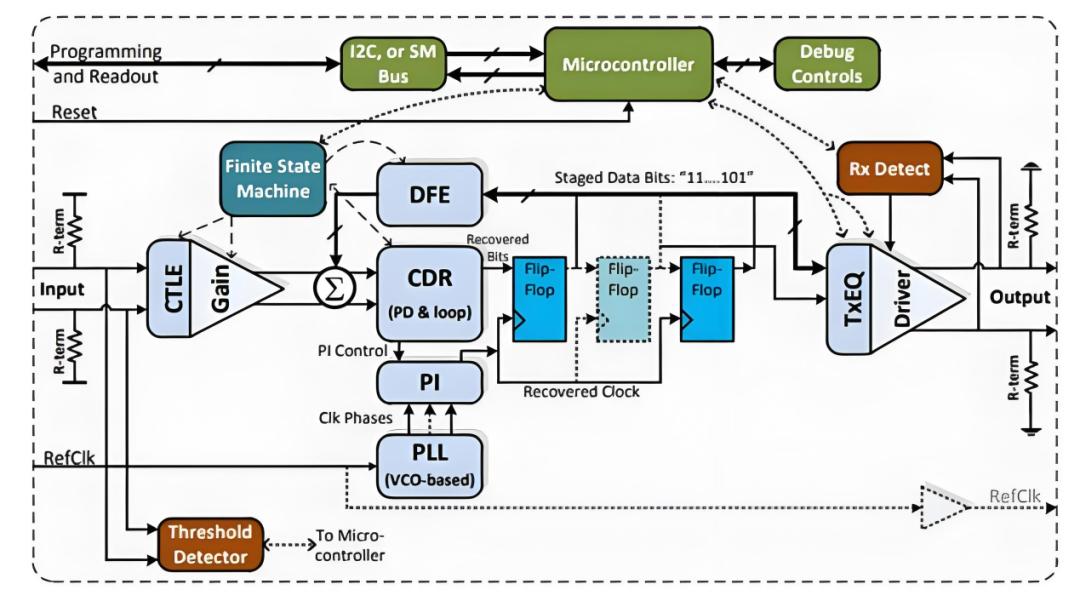

Retimer芯片是一种混合信号模拟/数字芯片,其原理是使用内部的时钟恢复电路,重新定时输入信号以消除时钟偏移和抖动,并校正信号的相位和时间偏差(jitter)。它可以延长接口的传输距离并提高信号质量,PCIe Retimer芯片主要解决数据中心、服务器通过PCIe协议在数据高速、远距离传输时,信号时序不齐、损耗大、完整性差等问题。

Retimer芯片内部构成(图源:PCI-SIG官网)

相比于市场其他技术解决方案,现阶段Retimer芯片的解决方案在性能、标准化和生态系统支持等方面具有一定的比较优势。值得一提的是,Retimer芯片可以灵活地切换PCIe或CXL模式,更符合未来CXL互连趋势。

这种功能特性,使其通用服务器与AI服务器市场天然具备高价值。

在通用服务器领域,随着云计算、大数据中心的扩张,PCIe 5.0及以上版本服务器渗透率的快速提升,每台服务器需搭载2-4颗Retimer芯片(用于CPU与PCIe插槽、高速存储的连接),叠加边缘计算服务器的增长,其市场需求呈指数级上升。

此外,随着AI浪潮的兴起,AI服务器成为Retimer芯片主要增量应用场景之一。

据了解,AI服务器里 PCIe Retimer芯片的数量,与服务器配置的 GPU数量直接相关。这是因为GPU的通道数(lane)直接决定了PCIe链路的配比。

AI服务器中通常需要多块GPU协同运算,单台AI服务器常搭载4-8块甚至更多GPU,GPU与CPU、GPU之间的PCIe链路不仅长,还需同时传输海量训练数据——Retimer芯片正是破解“多GPU互连信号瓶颈”的关键,能让AI算力集群的协同效率大幅提升。

目前一台典型的配8块GPU的主流AI服务器需要8颗甚至16颗PCIe 5.0 Retimer芯片。

可见,Retimer芯片在AI时代与服务器领域拥有广阔的市场空间。

双寡头引领与多强竞逐“黄金赛道”

在PCIe高速互连的黄金时代,Retimer芯片市场形成了“双寡头引领、多强竞逐”的格局。

当前全球市场主要由服务器数模芯片厂商与传统模拟巨头共同分割,其中AsteraLabs与澜起科技的竞争尤为瞩目——前者凭借PCIe 5.0的先发优势占据全球主要份额,后者则以国产替代之势快速崛起,二者共同主导高端市场;谱瑞(Pericom)、IDT(被瑞萨收购)凭借技术积累占据传统阵地,而TI、Microchip等巨头则以通用型产品覆盖中低端领域,构成多层次竞争生态。

追溯发展历程,不同厂商的技术路径呈现鲜明差异。

作为市场早期入局者,谱瑞凭借 PCIe 3.0/4.0 时代的先发优势,其产品率先通过 Intel、AMD 等主流平台认证,成为服务器厂商的核心供应商,目前已形成覆盖PCIe 3.0-5.0的完整产品线,相关芯片的传输速率和低延迟特性站稳高端市场。

IDT则依托在定时芯片领域的技术积累,早期在多代PCIe协议兼容上占据优势,被瑞萨收购后其Retimer技术与瑞萨的模拟芯片能力深度整合,持续向PCIe 5.0/6.0领域延伸。

美国厂商AsteraLabs凭借“Smart Retimer”概念打破传统,其PCIe 4.0产品2024年实现量产,PCIe 5.0产品通过管脚兼容设计降低客户升级成本,并联合云服务厂商建立Cloud-Scale Interop Lab生态,快速占领AI服务器市场,成为当前4.0/5.0时代的份额主导者。

国内龙头澜起科技则展现出强劲的替代能力,从内存接口芯片领域跨界切入后,其PCIe 4.0 Retimer已稳定量产,PCIe 5.0产品自2024年起连续两个季度出货翻倍,在手订单饱满,更于2025年初率先推出PCIe 6.x/CXL 3.x Retimer 并送样,传输速率达 64GT/s,技术壁垒持续强化。

传统模拟巨头则以差异化策略分食市场。TI凭借广泛的工业客户基础,提供适配多场景的通用型Retimer芯片,虽未专注高端AI领域,但在中低速PCIe链路中仍具竞争力;Microchip早在2020年便发布支持PCIe 5.0与CXL 2.0的Retimer系列,其产品已成为英特尔平台参考设计的常用选择,在传统服务器市场占据一席之地。

在国产替代与技术升级的双重红利下,这场围绕高速互连的竞逐正迎来机遇期。

有行业数据预测显示,2025年全球PCIe Retimer芯片市场规模将达到18亿美元。在此市场潜力下,Retimer芯片一度被视为“PCIe高速化浪潮下的必选组件”,是半导体产业链中与AI算力、服务器扩张深度绑定的“黄金赛道”。

nvtel联盟,带来微妙变化

然而,这场由英伟达与英特尔联手掀起的技术革命,或可能给PCIe Retimer市场带来微妙的变化。

当英伟达以50亿美元战略入股英特尔,并开放NVLink技术生态,这位PCIe标准的长期挑战者终于获得了撬动产业格局的关键支点——而英特尔作为PCIe协议的奠基者选择“倒戈”,更让这场冲击具备了颠覆技术阵营的深层力量。

首先是技术代差的碾压效应首当其冲。据了解,第五代NVLink技术已实现1.8TB/s的总带宽,是PCIe Gen5的14倍以上,且凭借芯片级集成设计将信号传输损耗降至最低。这种优势直接消解了PCIe Retimer的价值。例如,在英伟达GB200 NVL72机架系统中,576个GPU通过NVLink形成超1PB/s的全域带宽,无需任何信号补偿芯片即可实现稳定互连;而传统方案中,8GPU AI服务器需配置8-16颗PCIe 5.0 Retimer才能避免信号失真。

NVLink为x86架构提供了比传统PCIe更高带宽、更低延迟的互联能力,这可能会改变数据中心内部的计算和数据流动模式。

当黄仁勋在发布会上强调“要把最好的CPU和最好的GPU通过NVLink结合”时,实际已宣告了高速互连领域“补偿时代”的终结。

更致命的是,英伟达GPU在AI时代具有绝对的统治力,在独立显卡市场占据92%份额,PC用GPU份额也提升至24%,而AI训练场景几乎完全依赖其芯片。在数据中心领域,定制化NVLink x86 CPU将替代通用PCIe接口方案;个人计算领域,英特尔集成RTX GPU芯粒的SoC将减少对独立PCIe显卡的依赖。

另一方面,Retimer芯片的主要作用就是 “信号放大”。当PCIe信号在长距离传输中衰减时Retimer会接收、重构并重新发送信号,确保数据完整性。当服务器采用模块化设计,CPU和GPU分散在不同板卡上时,长距离的信号传输就必须依赖Retimer。如果CPU和GPU在同一块大型主板上,信号链路较短,则Retimer的用量就会减少。

总之,当开发者围绕NVLink优化软件栈,当云服务商批量部署NVLink集群时,PCIe Retimer的生存空间将被系统性挤压。

此外,生态迁移的连锁反应更具破坏性。英特尔将为英伟达定制x86 CPU,这些芯片将直接集成NVLink接口进入AI基础设施平台——这意味着一部分PCIe服务器市场将转向NVLink架构。

此前,要将一个私有协议推向行业标准,对抗开放的PCIe联盟,单靠英伟达一家虽颇有成效,但终归独木难支。而在这盘大棋中,Intel正是那个最关键、也最微妙的“棋子”。一旦Intel的服务器CPU开始支持NVLink,整个服务器生态系统将被迫跟进,这将极大加速NVLink的普及,形成事实上的行业标准。

如果这套方案真正跑通了,不难想象,未来的AI服务器设计、主板布局、芯片接口都将围绕NVLink展开,任何想要接入这个高性能计算生态的芯片(无论是CPU还是其他AI芯片),都必须兼容NVLink Fusion协议。这将形成一种强大的捆绑效应,将整个产业链从主板制造商、服务器厂商到最终用户,都牢牢锁定在英伟达的生态圈内。而一旦掌握了协议主导权,英伟达便可以通过授权、认证等方式,从每一个接入其生态的硬件中获利,成为数据中心时代的“高通”。

乍看之下,“英伟达入股Intel”的动作似乎是GPU霸主向CPU巨头的示好或渗透,意图补全其在通用计算领域的版图。但这不仅是一次投资,更是一场意图重塑未来数据中心底层协议、构建英伟达除了CUDA之外的第二道“护城河”的深远布局,对NVLink互联协议的超前布局。

这场冲击的本质,是产业标准从“通用兼容”向“垂直整合”的范式转移——当CPU与GPU的领导厂商直接定义互连协议,第三方Retimer芯片的价值自然大幅缩水,市场格局的重构或已露端倪。

换个角度思考,英伟达与英特尔的合作在战略协同层面也具备优势: 面对共同的挑战(如ARM架构在服务器市场的侵蚀、AMD在CPU和GPU领域的攻城略地),Intel与英伟达可以形成“CPU+GPU/互联”的nvtel联盟,共同定义下一代计算平台的架构。

写在最后

综合来看,当英伟达携NVLink技术入股英特尔,以“协议定义护城河”的战略升维撬动高性能计算的架构格局时,PCIe Retimer市场确实告别了过去“高速增长无虞”的黄金时代——这场由两大芯片巨头联手掀起的互连革命,可能会短暂影响依托PCIe链路站稳脚跟的Retimer芯片。

但这仅仅是一种初步见解,因为在很多分析人士看来,PCIe Retimer的市场空间,仍扎根在诸多无法被NVLink完全覆盖的场景里——在长距离传输与复杂拓扑中,GPU服务器的机头与机尾、GPU与交换机的铜缆连接,仍需它以自适应均衡能力抵消信号衰减;在非GPU设备互联领域,SSD、网卡与CPU的高速链路,尤其是复杂布线场景下,Retimer仍是保障数据“零丢包”的关键;更不用说采用OAM架构的服务器,其通用基板(UBBP)设计天然依赖Retimer芯片维持信号完整性。

这种不可替代性,也让PCIe Retimer市场底色尚存,依然是AI时代算力网络中“不可或缺的拼图”。