1、安路科技“防止FPGA配置码流被DPA攻击的电路及包括该电路的FPGA”专利公布

2、胜科纳米“一种芯片缺陷区域确定方法、装置、设备及存储介质”专利公布

3、钰泰半导体“马达驱动芯片高侧功率管的栅极电压检测及控制驱动电路”专利公布

4、盛景微“基于污染源扩散理论的低可靠性芯片识别方法及装置”专利公布

5、飞骧科技“基于边收缩技术的电路预处理方法、系统及相关设备”专利获授权

1、安路科技“防止FPGA配置码流被DPA攻击的电路及包括该电路的FPGA”专利公布

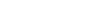

天眼查显示,上海安路信息科技股份有限公司“防止FPGA配置码流被DPA攻击的电路及包括该电路的FPGA”专利公布,申请公布日为2024年10月11日,申请公布号为CN118761104A。

本申请涉及集成电路技术领域,公开了一种防止FPGA配置码流被DPA攻击的电路及包括该电路的FPGA。防攻击电路包括:真随机数发生器、伪随机数发生器、移位寄存器和控制电路;真随机数发生器用于产生种子到伪随机数发生器并分别产生第一随机数和第二随机数到移位寄存器;伪随机数发生器进行移位操作,和/或根据种子生成伪随机序列并产生功耗;移位寄存器根据第一随机数进行移位数随机的移位操作以在FPGA配置码流数据移位过程中产生随机强度的功耗,和/或根据第二随机数进行时钟信号延迟随机的移位操作以产生随机延迟的功耗;控制电路用于根据预设配置控制伪随机数发生器和移位寄存器。本申请可以在FPGA配置码流解密过程中加入功耗干扰,防止DPA攻击。

2、胜科纳米“一种芯片缺陷区域确定方法、装置、设备及存储介质”专利公布

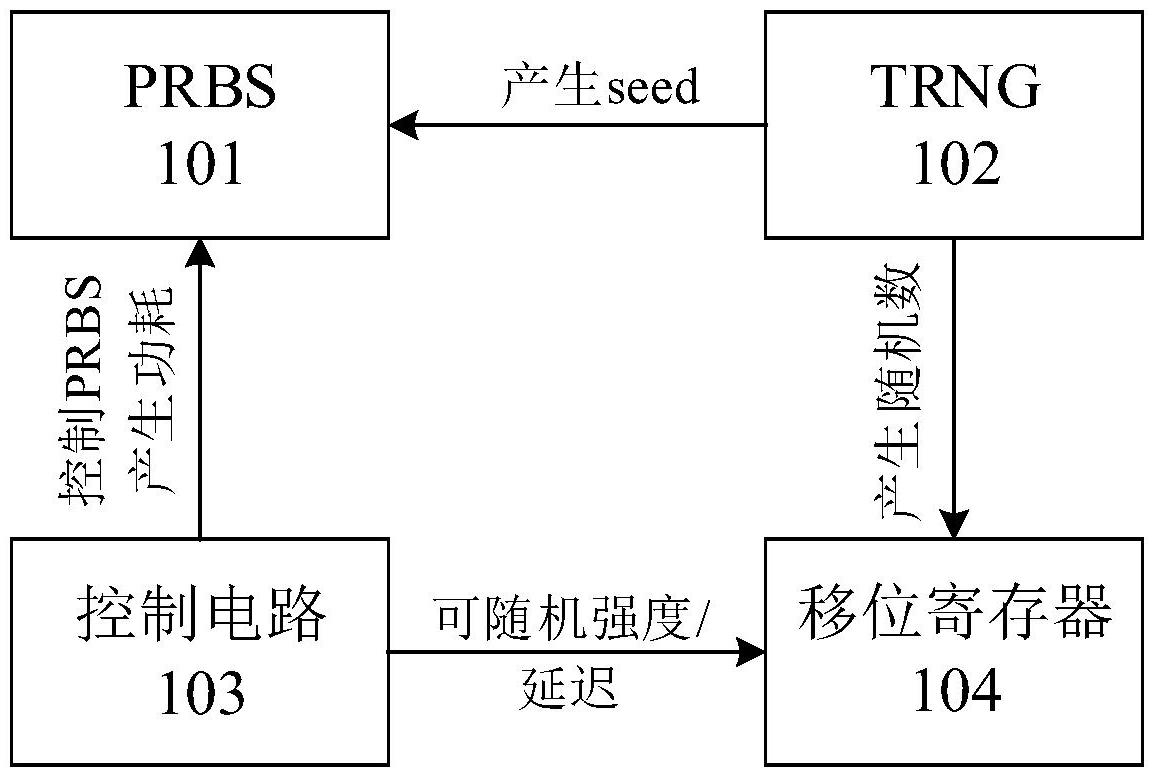

天眼查显示,胜科纳米(苏州)股份有限公司“一种芯片缺陷区域确定方法、装置、设备及存储介质”专利公布,申请公布日为2024年10月11日,申请公布号为CN118762014A。

本发明公开了一种芯片缺陷区域确定方法、装置、设备及存储介质。该方法包括:获取目标芯片对应的原始芯片图像;将原始芯片图像进行排列方向检测,确定图像切割方向,并将原始芯片图像进行分割处理,获得第一分割图像;基于图像切割方向的相互垂直方向,将第一分割图像进行像素值统计处理,获得分割投影图像;根据分割投影图像,确定估计周期长度,并基于估计周期长度,将第一分割图像进行裁剪处理,获得第二分割图像。将当前第二分割图像与其他第二分割图像进行对比,确定存在缺陷的目标第二分割图像,进而确定目标芯片的缺陷位置,以准确确定芯片缺陷区域。该方法无需人工参与,降低人工成本,同时可以提升缺陷区域的检测效率。

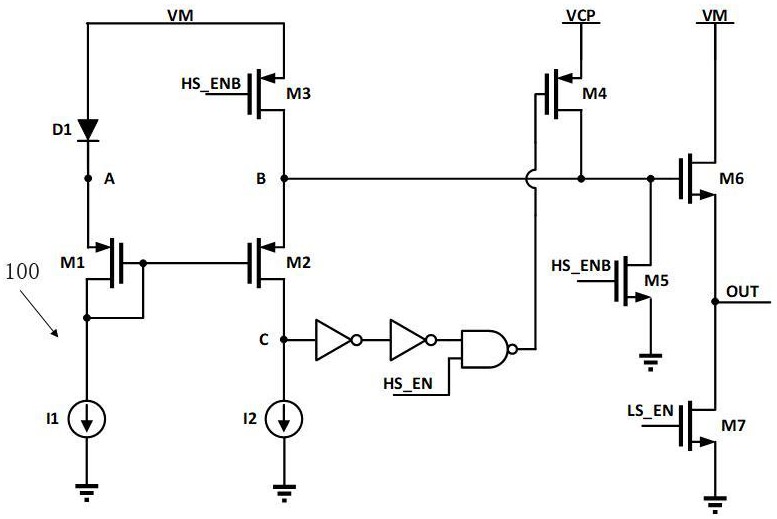

3、钰泰半导体“马达驱动芯片高侧功率管的栅极电压检测及控制驱动电路”专利公布

天眼查显示,钰泰半导体股份有限公司“马达驱动芯片高侧功率管的栅极电压检测及控制驱动电路”专利公布,申请公布日为2024年10月11日,申请公布号为CN118763879A。

本发明提供一种马达驱动芯片高侧功率管的栅极电压检测及控制驱动电路,包括:辅助上拉开关管,在高侧驱动管的控制信号的反相信号为低电平时导通,以将高侧驱动管的栅极电压从0上拉至电源电压;主上拉开关管,在栅极电压检测系统的输出信号和高侧驱动管的控制信号均为高电平时导通,以将高侧驱动管的栅极电压充至高于电源电压的额定电压,否则关断;栅极电压检测系统包括电流模比较器,第二输入端连接高侧驱动管的栅极电压,第一输入端连接二极管类器件的低压侧,电流模比较器在第一输入端的电位低于第二输入端的电位时,输出高电平;否则输出低电平。本发明的电路能够减小电荷泵的驱动时间,减轻用于提供额定电压的电荷泵的负载压力。

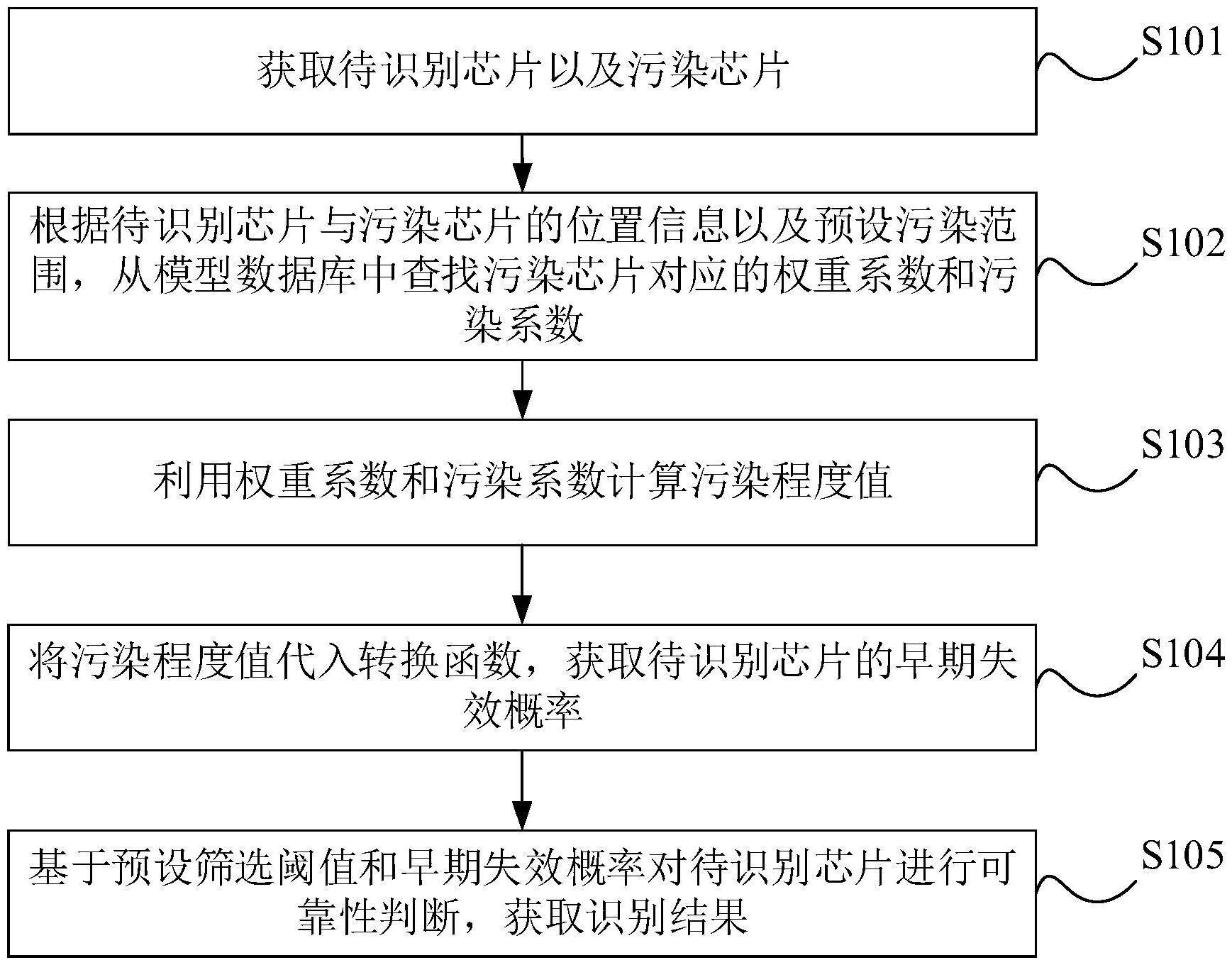

4、盛景微“基于污染源扩散理论的低可靠性芯片识别方法及装置”专利公布

天眼查显示,无锡盛景微电子股份有限公司“基于污染源扩散理论的低可靠性芯片识别方法及装置”专利公布,申请公布日为2024年10月11日,申请公布号为CN118761427A。

本发明提供了基于污染源扩散理论的低可靠性芯片识别方法及装置。其中,包括:获取待识别芯片以及污染芯片;根据待识别芯片与污染芯片的位置信息以及预设污染范围,从模型数据库中查找污染芯片对应的权重系数和污染系数;模型数据库包括:第一数据库和第二数据库,第一数据库用于存储相关位置信息,第二数据库用于存储相关权重系数和相关污染系数;利用权重系数和污染系数计算污染程度值;将污染程度值代入转换函数,获取待识别芯片的早期失效概率;基于预设筛选阈值和早期失效概率对待识别芯片进行可靠性判断,获取识别结果;第二数据库和转换函数均基于优化遗传算法优化训练得到。提高了低可靠性芯片识别的稳定性和准确性,降低了良品损失。

5、飞骧科技“基于边收缩技术的电路预处理方法、系统及相关设备”专利获授权

天眼查显示,深圳飞骧科技股份有限公司“基于边收缩技术的电路预处理方法、系统及相关设备”专利获授权,授权公告日为2024年10月11日,授权公告号为CN118536319B。

本发明提供一种基于边收缩技术的电路预处理方法、系统及相关设备,所述方法包括:基于原始等效电路构建关于其中不同电路元件之间的连接关系的电路连接列表;遍历所述电路连接列表,基于边收缩方法对不同的所述连接关系进行可合并判断,并对所述电路连接列表中的所述连接关系进行重排序,得到有序电路连接列表;遍历所述有序电路连接列表,基于边收缩方法对不同的所述连接关系进行可合并判断,并对所述有序电路连接列表中的所述连接关系进行合并,得到合并电路连接列表;基于所述合并电路连接列表,将不同的所述电路元件进行连接,得到简化等效电路。本发明降低了电路散射参数矩阵的计算耗时。