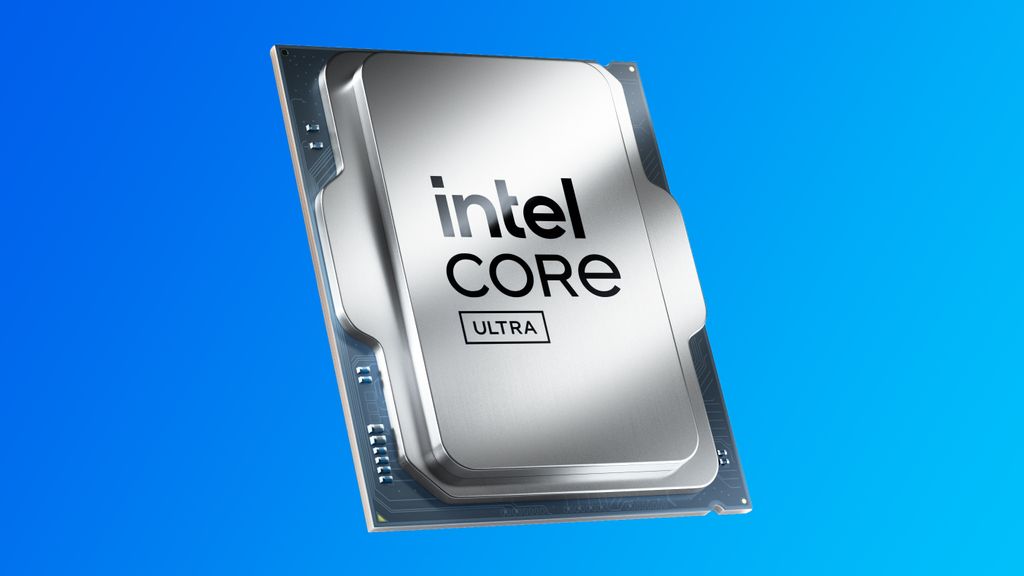

(图片来源:英特尔)

英特尔最新发布的Arrow Lake架构芯片照片,详尽展示了其小芯片(tile)设计的独特魅力。X平台的Andreas Schiling通过一系列高清照片,让我们得以窥见Arrow Lake内部各个基础芯片的布局以及计算核心的精妙排布。

首图呈现的是英特尔桌面级Core Ultra 200S系列CPU的完整面貌。其中,计算芯片傲立左上角,IO芯片稳坐底部,而SoC芯片与GPU芯片则并肩于右侧。左下角与右上角巧妙地布置了两个填充芯片,它们的主要作用是增强结构的稳固性。

@highyieldYT对#ArrowLake的深度剖析亮点多多 pic.twitter.com/WFUG0xVaFEMay 5, 2025

计算芯片采用了台积电最先进的N3B节点技术,其面积达到了117.241平方毫米。而IO芯片与SoC芯片则选用了台积电稍旧的N6节点,面积分别为24.475平方毫米和86.648平方毫米。所有基础芯片均基于英特尔22nm FinFET节点制造的底层芯片。值得注意的是,Arrow Lake是英特尔首次在基础芯片之外,全面采用竞争对手节点制造的架构。

接下来的照片则深入展示了Arrow Lake中次级基础芯片的所有子组件。IO芯片内置了Thunderbolt 4控制器/显示PHY、PCIe Express缓冲器/PHY以及TBT4 PHY。SoC芯片则集成了显示引擎、媒体引擎、更多PCIe PHY、缓冲器以及DDR5内存控制器。而GPU芯片则内置了四个Xe GPU核心和一个Xe LPG(Arc Alchemist)渲染切片,彰显其强大的图形处理能力。

最后一张照片则揭示了英特尔为Arrow Lake设计的最新核心配置,这一配置与之前的混合架构有所不同。在Arrow Lake中,英特尔创新地将E核夹在了P核之间,而非将它们全部置于单独的集群中。据称,这种设计有助于减少热点现象。八个P核中,四个位于芯片边缘,另四个则处于芯片中心。四个E核集群(每个集群含四个核心)被巧妙地布置在外层P核与内层P核之间。

Schiling的芯片照片还细致展示了Arrow Lake的缓存布局。每个P核均配备了3MB的L3缓存(总计36MB),而每个E核集群则拥有3MB的L2缓存,其中两个核心直接共享1.5MB。一个互连桥不仅连接了两个L2缓存集群(及其关联核心),还负责将每个核心集群与环形代理紧密相连。英特尔在Arrow Lake上的另一项重大升级是将E核集群与P核共享的L3缓存相连,从而有效地为E核提供了一个L3缓存。

Arrow Lake无疑是英特尔迄今为止最为复杂的架构之一,也是该公司首次将小芯片设计风格引入桌面市场。然而,英特尔首次尝试推出基于小芯片的桌面级产品并未获得广泛好评,主要原因在于连接所有基础芯片的互连存在延迟问题。英特尔正积极通过固件更新来解决这一难题。尽管如此,其当前实现仍难以与AMD的竞争对手Ryzen 9000 CPU(如9800X3D)相抗衡,在游戏性能方面也未能超越其上一代第14代处理器(如14900K)。

尽管如此,转向小芯片设计方法将为英特尔在未来提供更多优化架构的可能性,并且效率更高。每个基础芯片均可独立开发,并可根据需要采用不同的节点制造,这不仅有助于提高产量、优化开发流程,还能有效降低生产成本。