(图片来源:Tom's Hardware)

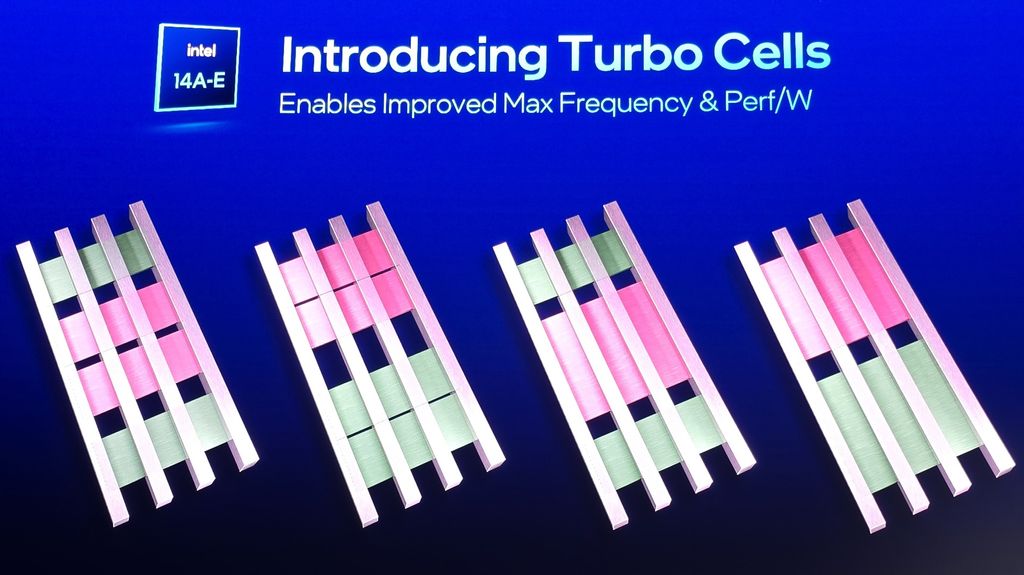

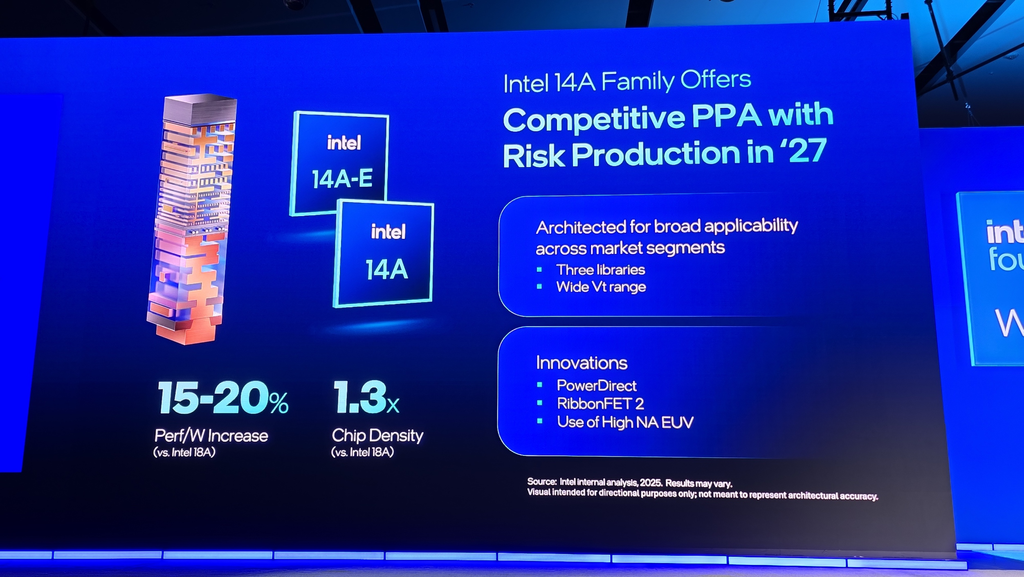

在加利福尼亚州圣何塞举办的Intel Foundry Direct 2025活动上,英特尔公布了一系列重要信息,并详细分享了即将于2027年投入风险生产的14A工艺节点性能指标。该节点预计功耗将降低高达35%。此外,英特尔还揭开了其全新的Turbo Cell技术的神秘面纱,这是一种高度可定制的设计方案,旨在实现CPU最大频率并提升GPU关键速度路径的性能。

(图片来源:Tom's Hardware)

(图片来源:Tom's Hardware)

14A和14A-E节点作为公司18A节点的后继者,展现了显著的性能提升。英特尔透露,与18A相比,14A每瓦性能将提升15%至20%,这意味着在相同功耗下可获得更高的时钟速度,或在保持性能不变的情况下降低25%至35%的功耗。这一进步主要得益于英特尔创新的直接接触背面电源传输网络——PowerDirect(更多详情见此处)。

英特尔还为该节点增加了其他新特性,如更宽的阈值电压(Vt)范围,以实现更灵活的电压/频率调节。

工艺路线图(图片来源:英特尔)

工艺路线图(图片来源:英特尔)

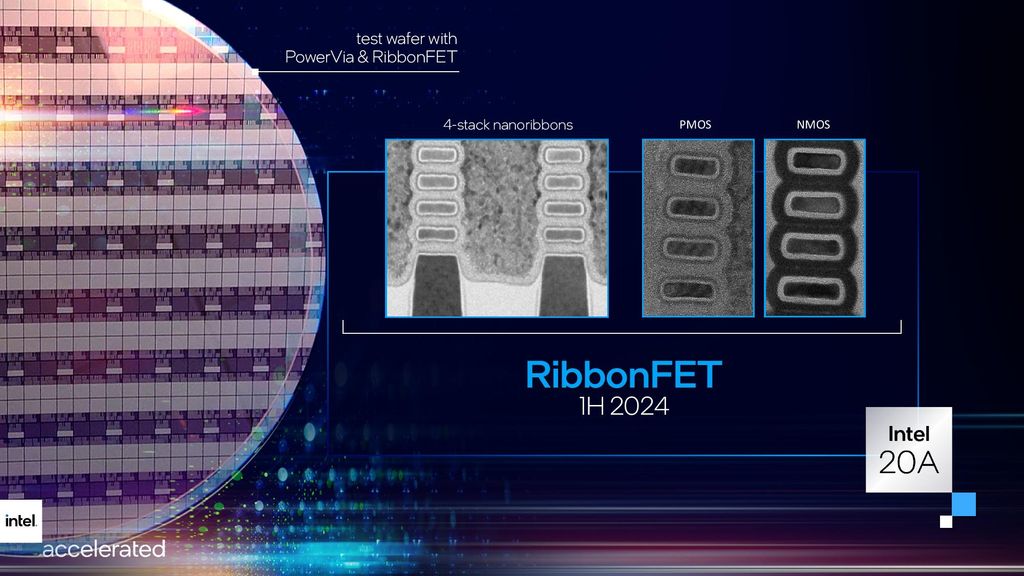

与18A节点相比,14A节点的晶体管密度提升了1.3倍。英特尔还对其RibbonFET晶体管进行了升级,现称为“RibbonFET 2”。虽然新一代RibbonFET的详细信息尚未公布,但通常设计通过采用四个完全被栅极包围的堆叠纳米片(如上方nmos和pmos晶体管的横截面所示),来提供更高的晶体管密度和更快的切换速度。

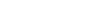

Turbo Cells与关键路径优化

英特尔的Turbo Cells技术是一项复杂但功能强大的创新。Turbo Cells可用于多种场景,但英特尔特别强调,它们将专门应用于CPU和GPU的关键路径,即速度路径,这背后有着充分的理由。

处理器内的时序路径是信号在正常运行时通过导线和逻辑门传播的路径。然而,信号延迟可能会影响处理器的时钟时序。关键路径是其中延迟最长的路径,因此成为限制整体性能的关键因素。

由于处理器依赖于时钟信号运行,最慢的关键路径决定了整个芯片的最高可能频率,从而成为性能瓶颈。传统上,芯片设计师会通过在这些区域使用更高速度的晶体管来应对这一问题,但这会降低晶体管密度并增加功耗,因为更快的晶体管泄漏更多能量。全新的Turbo Cells为芯片架构师提供了更精细的工具,以缓解关键路径问题。

14A节点配备了三个不同的标准单元库,这些库包含针对特定工艺节点预设计的逻辑门和电路元件(由晶体管构建)。设计师在设计流程中利用电子设计自动化(EDA)软件工具调用这些库,通常以行形式布局。

英特尔的14A节点包括三个库:“高”库针对高频(低密度)进行优化,“中”库针对每瓦性能进行优化,而“短”库则专注于密度,适用于对面积和功耗敏感的应用。目前,英特尔尚未分享各库的密度信息。

在CPU和GPU中大量使用短库,以在保持功耗可控的同时封装尽可能多的晶体管。这正是英特尔全新Turbo Cells技术大展身手的地方。

(图片来源:Tom's Hardware)

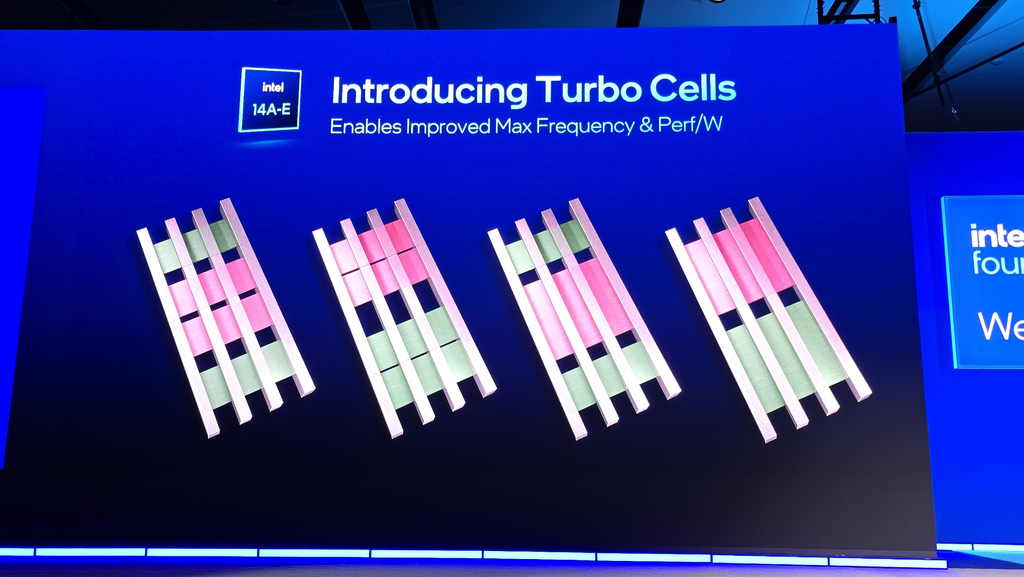

Turbo Cells通过增加短库在创建双高库(两个标准行的高度)时的晶体管驱动电流来提升性能,同时保持高密度排列以实现最佳面积效率。

上图展示了nmos和pmos条带/纳米片(粉色和绿色)的四种不同排列方式,它们具有不同的宽度和配置,以优化不同场景下的驱动电流。条带的宽度可以调整,或者可以独立合并以创建超宽条带,从而实现最大的驱动电流传递。

英特尔表示,Turbo Cells最终能够在同一设计块内将更快且功耗较低的单元与功耗较低的单元混合使用,从而为任何给定用例创建理想的功耗、性能和面积(PPA)平衡。

关键路径是最终的瓶颈,可以将其视为链条中最薄弱的环节。英特尔的全新Turbo Cells技术旨在通过加速这些路径来提升整体处理器性能,同时避免了传统解决关键路径问题所需的妥协。我们期待在2027年见证这一技术的实际表现。