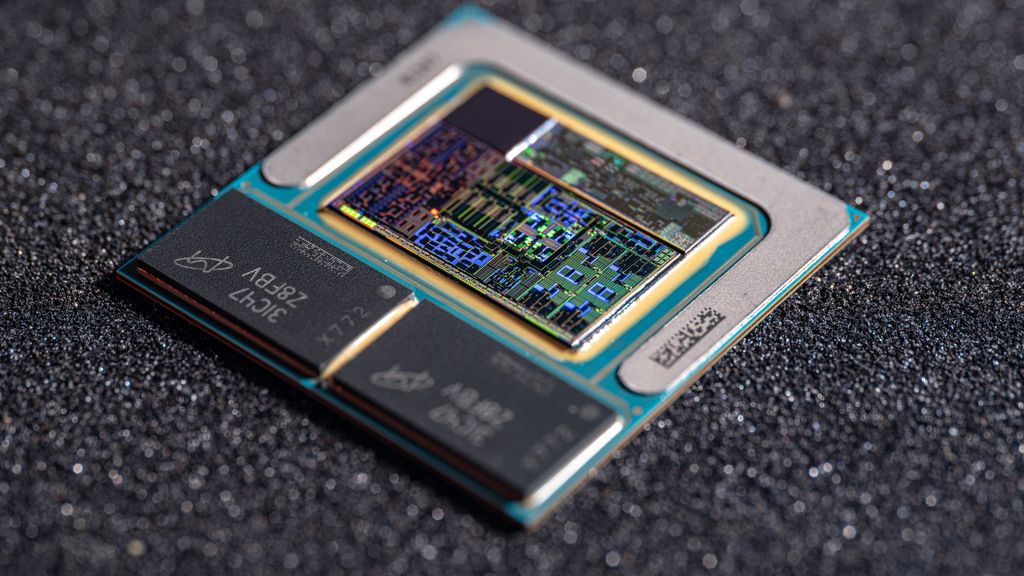

(图片来源:Fritzchen Fritz)

Lunar Lake凭借其独特的融合设计——将Arm基SoC中常见的超高效设计与x86的成熟架构相结合,无疑在市场上引起了轰动。知名硬件爱好者Fritzchen Fritz,以拍摄CPU极尽详细且高分辨率的芯片照片著称,他近期剖析了一个Lunar Lake样本,为我们揭示了其内部结构及Intel的精湛工艺。

Lunar Lake的开发过程,是Intel在成本控制与产品卓越性之间寻求平衡的一次挑战。其成果与高通公司的Arm基产品高度相似,并能有效与Apple Silicon竞争。然而,创新总是伴随着成本,搭载Lunar Lake的笔记本电脑价格依然维持在四位数。前首席执行官Pat Gelsinger甚至将其描述为“一次性”设计,这或许解释了为何Intel的泄露路线图中未提及后续产品。

尽管与Arrow Lake共享核心微架构和工艺节点,但Intel在Lunar Lake上采取了截然不同的开发策略。由TSMC N3B制造的Compute Tile配备了四个基于Lion Cove的性能(P)核,共享12MB的L3缓存,每个P核还拥有2.5MB的专属L2缓存。与Arrow Lake不同,基于Skymont的能效核心集群(E)并未共享L3缓存池,而是独立存在于一个拥有4MB专用L2缓存的“低功耗岛”上。E核旁边是NPU(神经处理单元),据推测拥有六个NCE(神经计算引擎),提供近48 TOPS的AI性能。

Compute Tile还整合了一个基于Battlemage的集成GPU,最多包含八个Xe2-LPG核心及Media Engine。Intel通过将所有关键处理元件封装于单一芯片内,显著降低了芯片间通信的延迟和功耗。此外,Intel还在内存控制器旁加入了一个8MB的系统级缓存(SLC),与Arm SoC类似,该缓存由CPU核心、集成GPU、NPU及Media Engine共享。为进一步强化集成度并减少延迟,内存物理层直接置于Compute Tile之上,紧邻作为SoC主内存的两个封装内、焊接且不可升级的LPDDR5x-8533 IC(16GB或32GB)。

位于Compute Tile下方的是基于TSMC N6工艺的Platform Controller Tile及一个用于增强结构刚性的虚拟tile。尽管内部代号为Lunar Lake的SoC Tile,但Platform Controller Tile可视为Arrow Lake的I/O Extender Tile的对应物。该芯片封装了关键的HSIO和LSIO组件,如USB、Thunderbolt、PCIe 4.0/5.0接口,以及蓝牙和Wi-Fi连接。所有这些芯片均坐落于22FFL有源中介层之上,并通过Intel的Foveros 3D封装技术紧密相连。

上述仅为芯片的总体规格概述;确切布局因芯片设计而异,且没有工程师的协助,我们无法确切了解Intel如何布局这些组件。所有注释均基于视觉线索的推测,不同分析师可能会有不同解读。

请在Google News上关注Tom's Hardware,以便在您的订阅中及时获取我们的最新新闻、分析及评论。别忘了点击关注按钮哦!